パワー半導体のコスト削減・環境負荷の低減・性能向上を実現!

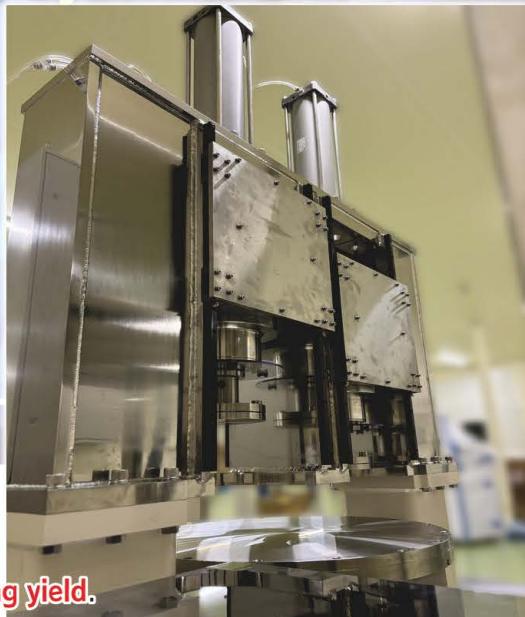

### » CARE法とは

大阪大学（山内特任教授、佐野教授）が考案した触媒基準エッチング法（CARE法）は、加工変質層（潜傷）が発生しない原子レベルの平坦化が可能な世界初の技術で、スラリーを使用しない画期的な次世代半導体製造のキープロセスとして注目されています。

\*弊社は、大阪大学が保有する特許2件の独占実施権を得ています。

### » CARE法の効果

#### ① コスト削減（歩留まり向上）

SiC等の新材料は、エピ膜を成膜して利用されていますが、この表面にはナノレベルのピットやバンプ、発見困難な潜傷が多数存在し、デバイスとなった時点での不良率は40%に達しています。

CARE法はこれらを除去し、歩留まり向上によるコスト削減を実現します。

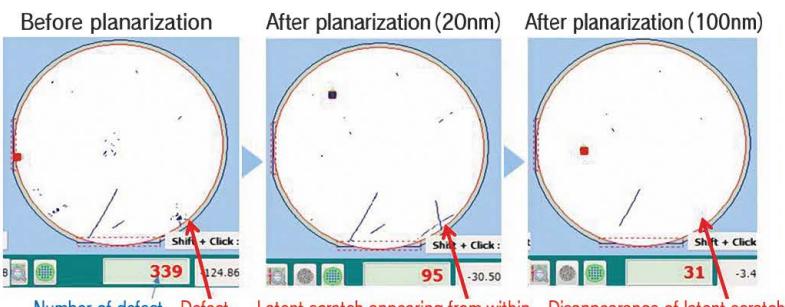

#### エピ成膜前に平坦化を行う方法

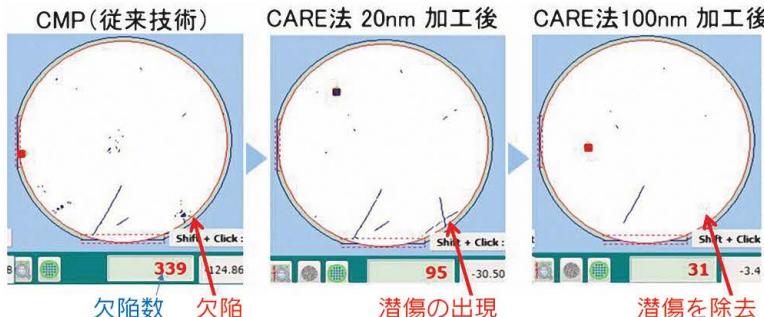

CARE法による潜傷の除去結果 表面検査画像（レーザーテックSICA6X）

► 潜傷が除去され、欠陥数も大きく減少 ( $339 \Rightarrow 95 \Rightarrow 31$ )

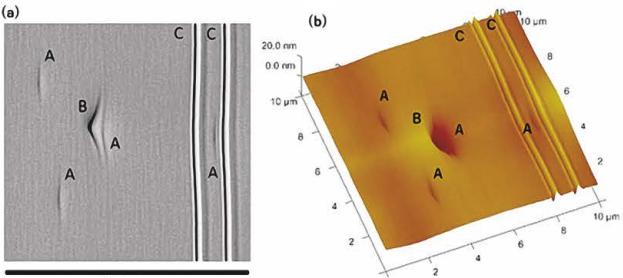

#### エピ成膜後に平坦化を行う方法

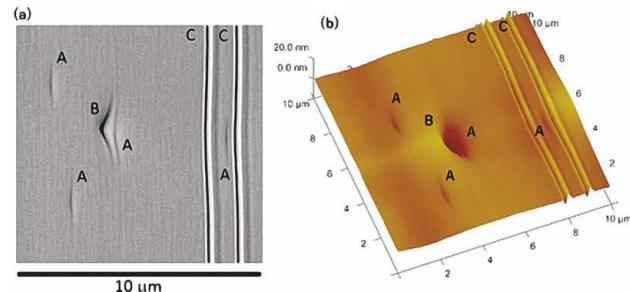

エピ膜上の欠陥の電子顕微鏡写真（アイシーソリューションズより一部引用）

エピ膜上の欠陥はCMPで対応困難

► CARE法なら除去可能

►►► Siと比較して100倍高いと言われるコストを低減させることができます。◀◀◀

#### ② 環境負荷の低減

CARE法は、CMPで使用されるスラリーを使用せず、水で平坦化を実現することから、環境負荷を大きく低減するクリーンな技術です。

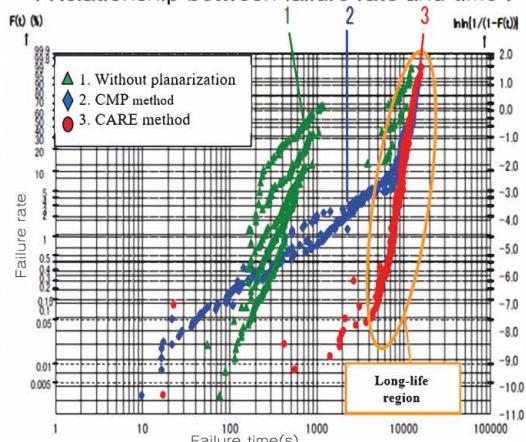

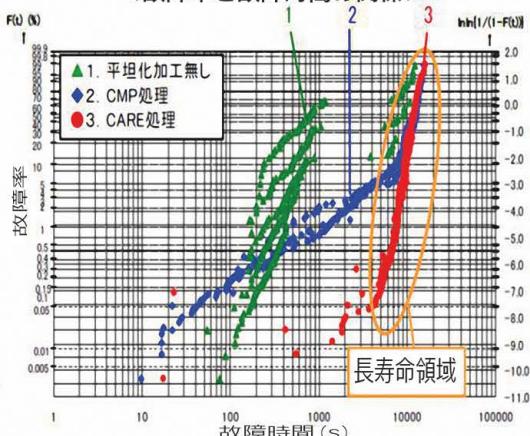

<故障率と故障時間の関係>

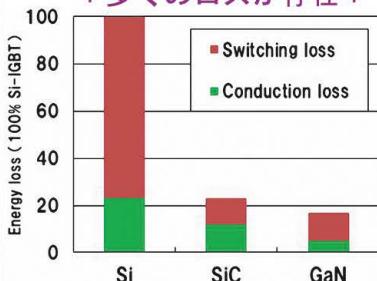

\*多くのロスが存在\*

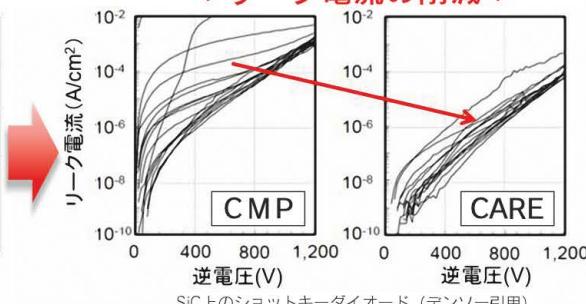

\*リーケ電流の削減\*

# CARE TEC®

Cost reduction, reduced environmental impact, and improved performance for power semiconductors!

## Next-generation semiconductor substrate Planarization System

### » What is the CARE method?

The catalyst-referred etching (CARE) method, which was devised by Osaka University (Professor Yamauchi and Sano), is the world's first technology to enable planarization of substrates at the atomic level, where no affected layers (latent scratches) are formed.

It is drawing attention as a **revolutionary slurry-free key process for next-generation semiconductor production.**

\* Osaka University has granted us exclusive usage rights to two patents.

### » Effects of the CARE method

#### ① Cost reduction (improved yield)

New materials, such as SiC, are used by forming epitaxial films, but many nano-level pits and bumps occur on their surfaces. Some latent scratches cannot be found easily, and the proportion defective reaches 40%.

The CARE method eliminates these and **achieves cost reduction by improving yield.**

##### Planarization before epitaxial film formation

Removing latent scratches by the CARE method Surface inspection image (Lasertec SICA6X)

► Latent scratches are eliminated and the number of defects is greatly reduced ( $339 \rightarrow 95 \rightarrow 31$ )

##### Planarization after epitaxial film formation

Electron micrograph of defects on epitaxial film (Source: ISEES-IIp.)

Defects on epitaxial layers are difficult to deal with CMP

► Removal possible with the CARE method

►►► It is possible to reduce costs, which are 100 times higher than Si. ◀◀◀

#### ② Reducing environmental impact

The CARE method **achieves planarization using water**, without using the slurry used in CMP. It is a **clean technology** that significantly reduces the environmental impact.

#### ③ Improved performance (Stable device manufacturing)

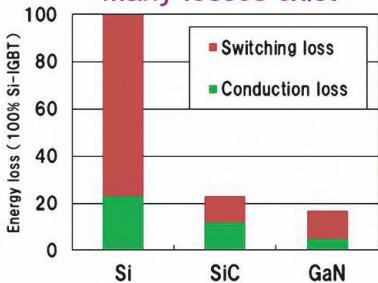

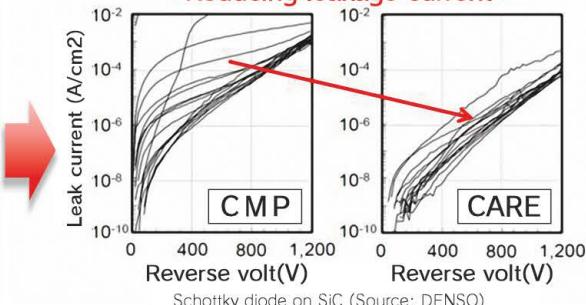

Power semiconductors used in cars are turned on and off tens of thousands of times per second, making **reducing leakage current** a challenge.

The CARE method makes it possible to significantly reduce leakage current, and it has also been confirmed that it **extends the life of the gate oxide film**.

\* Many losses exist \*

\* Reducing leakage current \*

< Relationship between failure rate and time >